Circuitos con compuertas lógicas

Introducción:

Se pueden realizar una serie de operaciones al juntar varios componentes que posean compuertas lógicas, mediante una serie de combinaciones que dan resultados a otras combinaciones, en este caso realizaremos una conversión de números binarios de 4 bits a otros números de 4 bits

Objetivos:

- Comprender la tabla de verdad de los montajes

- Comprobar la tabla de verdad de los montajes

Materiales

- 5 LED'S

- PROTOBOARDS

- CABLE

- 2 compuertas 7400

- 1 compuerta 7404

- 2 compuertas 7408

- 2 compuertas 7410

- 2 compuertas 7432

- 1 compuerta 7486

- Fuente D.C 5V

- 3 Dip Switch de 4 bits

- 16 resistencias de 1000 ohm

Montaje 1

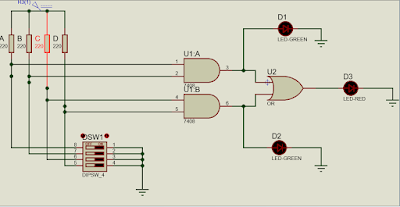

Figura 1. Montaje 1

En el Montaje de la Figura 1. se visualizan 4 entradas conectados a un Voltaje, utilizando lógica positiva. En la compuerta NAND U1:A , se visualiza el producto lógico entre las entradas A y B, en la compuerta NAND U1:B, se visualiza el producto lógico entre las entradas C y D, en el momento en el que A y B sea un High Voltage, se obtendrá como resultado en U1:A un High Voltage, de igual manera acontece lo mismo en la compuerta U1:B, cuando alguno de estos sea un High Voltage se encenderá el led conectado a la salida de la compuerta lógica, en base al resultado de cualquiera de las dos compuertas logicas, la compuerta OR U2, se obtendrá un High Voltage en el caso de que cualquiera de las dos compuertas NAND se produzca un High. Como se visualiza en la Tabla 1.

Tabla 1. Tabla Montaje 1

Vídeo 1. Explicación Montaje 1

Montaje 2

Figura 2. Montaje 2

En el Montaje de la Figura 2. se visualizan 4 entradas conectados a un Voltaje, utilizando lógica positiva, la compuerta U1 es una compuerta X-OR, se enfoca en la suma Lógica de la negación de una de las entradas (A'B+AB'), la compuerta U5 es una compuerta OR, realiza la suma lógica sin acarreo positivo (A+B), en la compuerta AND U2 , se obtiene el producto entre el resultado de U1 y la entrada C (A'B+AB')(C), la compuerta NOT U3 , negara la salida de la compuerta AND U2 ( (A'B+AB')(C))' , la compuerta NAND U6, realizara la negación del producto de la salida de la compuerta U5 y la entrada A ((A'B+AB')(A))', en la compuerta NAND U4, se realizara la negación del producto de las salidas de las compuertas U3 y U6. Como se logra visualizar claramente en la tabla de verdad de la Tabla 2.

Tabla 2. Tabla montaje 2

Vídeo 2. Explicación Montaje 2

Montaje 3

Figura 3, Montaje 3.

En el montaje de la Figura 3, se visualizan 3 entradas conectados a un Voltaje, utilizando lógica positiva la compuerta NAND de 2 entradas U3:A realizan la negación del producto entre A y B (AB)' , la compuerta NAND de 3 entradas U2:B se realiza la negación del producto entre A , C y la salida de la compuerta U3:A , la compuerta NAND de 3 entradas U2:C , se realiza la negación del producto de la entrada B, C y la salida de la compuerta U3:A , la compuerta NAND de 3 entradas U1:B realiza la negación del producto entre la entrada A , la salida de la compuerta U2:B y la salida de la compuerta U3:A, la compuerta NAND de entradas U1:C realizada la negación del producto U2:B , C y U2:C, U2:A realiza la negación del producto de las salidas U2:C , U3:A y la entrada A, la compuerta de la Salida U1:A, realiza la negación del producto entre las salidas de U1:B , U1:C y U2:A. Se visualiza la comprobación de la Tabla 3.

Tabla 3. Tabla Montaje 3

Vídeo 3. Explicación Montaje 3

Formato Físico:

Video 4, Formato Físico 3 montajes

Conclusión:

Analizar un circuito mediante su tabla de verdad, facilita la comprensión del mismo, ya que dentro de las mismas se ha de colocar la operación que produce cada componente, trayendo consigo una fácil visualización del problema a analizar.

Los montajes mediante integrados en compuertas lógicas tienden a ser muy tediosos debido a la gran cantidad de conexiones que estos poseen, ademas de esto la composición o estructuración de los mismos puede ocupar demasiado espacio.