Multiplexación Teclado

Materiales:

- Cable

- Protoboard

- Computador con PSoC Creator

Procedimiento:

Para esta práctica utilizamos la visualización dinámica, ésta consiste en encender uno a uno los leds que conforman la pantalla de visualización (7 segmentos en nuestro caso), y encenderlos uno a uno en un tiempo independiente, al subir a una frecuencia superior a los 60Hz, el ojo humano percibe la imagen que es originalmente dinámica como una imagen estática.

Se ha de utilizar la información utilizada previamente en el anterior informe de Visualización dinámica.

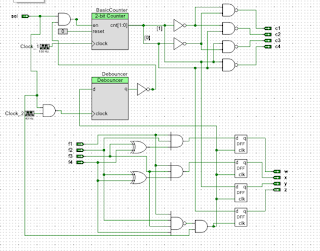

Fig 1. Multpliexacion del teclado

Para la correcta multiplexacion de nuestro teclado matricial se utilizaron multiplexores y demultiplexores para generar la división de los datos. Del mismo modo se utilizaron Deboucers. Tal como se logra visualizar en la figura 1.

En el circuito que nos permitía usar el teclado matricial normalmente se adiciono una compuerta AND que actuara como un selector permitiendo que el teclado funcione cuando nuestro selector se comporte como un “1” lógico y que el mismo no pueda funcionar cuando sea un “0” lógico.

Fig. 2. Negación de los relojes

En la fig 2. Se visualiza la acción de la negación de los relojes en el momento de seleccionar las diferentes opciones que brinda el teclado matricial. De esta manera los datos quedaran almacenados y se permitirá la futura edición de los mismos mediante un selector.

Fig 3. Multiplexor 2 a 1

Fig 4. Multiplexor 8 a 4

Como se logra visualizar en la Figura 3.se muestra la estructura básica de un mux 2 a 1. En la figura 4, mediante el uso de mux 2 a 1. Se puede diseñar un multiplexor de 8 a 4 , para que se permita la importación de datos en 4 secuencias.

Al momento de Multiplexar las señales de entrada, hemos de analizar nuestra segunda etapa. La cual consiste principalmente en la multiplicación de números de 4 bits. Este proceso se ha de realizar con compuertas AND y sumadores con acarreo positivo (sumadores completos)

Fig 5. Sumador Completo de 1 bit

En la Figura 5 se logra aprecia el funcionamiento de un sumador completo de 1 bit. El cual consiste en la suma de 2 números de cada uno de 1 bit. Para que en el caso especial en el que cada uno de estos sea un 1 Lógico se obtenga como resultado un 10.

Fig 5 .Sumador Completo de 4 bits

Para la suma de números de 4 bits se utiliza la misma logica del sumador de 1 bit. Ya que se tiene en cuenta un acarreo positivo posterior , ya que en el caso de que se posea este mismo no se genera un inconveniente al momento de realizar la operación de "1+1" con un acarreo positivo de 1. Ya que esta operación dará como resultado 11.

Fig 6. Multiplicador

Debido a que la multiplicación y la suma son operación afines podemos buscar la manera en que la suma consecutiva del numero de como resultado el numero deseado.

Después de obtenido el resultado de la multiplicación de los números de 4 bits , se busca la conversión de binario a decimal. Mediante el arreglo del integrado DN74185A.

Fig 7. Tabla de verdad 74185

El integrado 74185 permite la conversión de números binarios a decimales mediante el desplazamiento de los números luego de que estos superen el 9.

Fig 8. Arreglo de Integrados 3 digitos

El arreglo que se puede visualizar en la Figura 8 , permite el ordenamiento de números de 3 dígitos en decimal, separando de esta manera Unidades, Decenas y Centenas.